上海瑟如电子科技有限公司

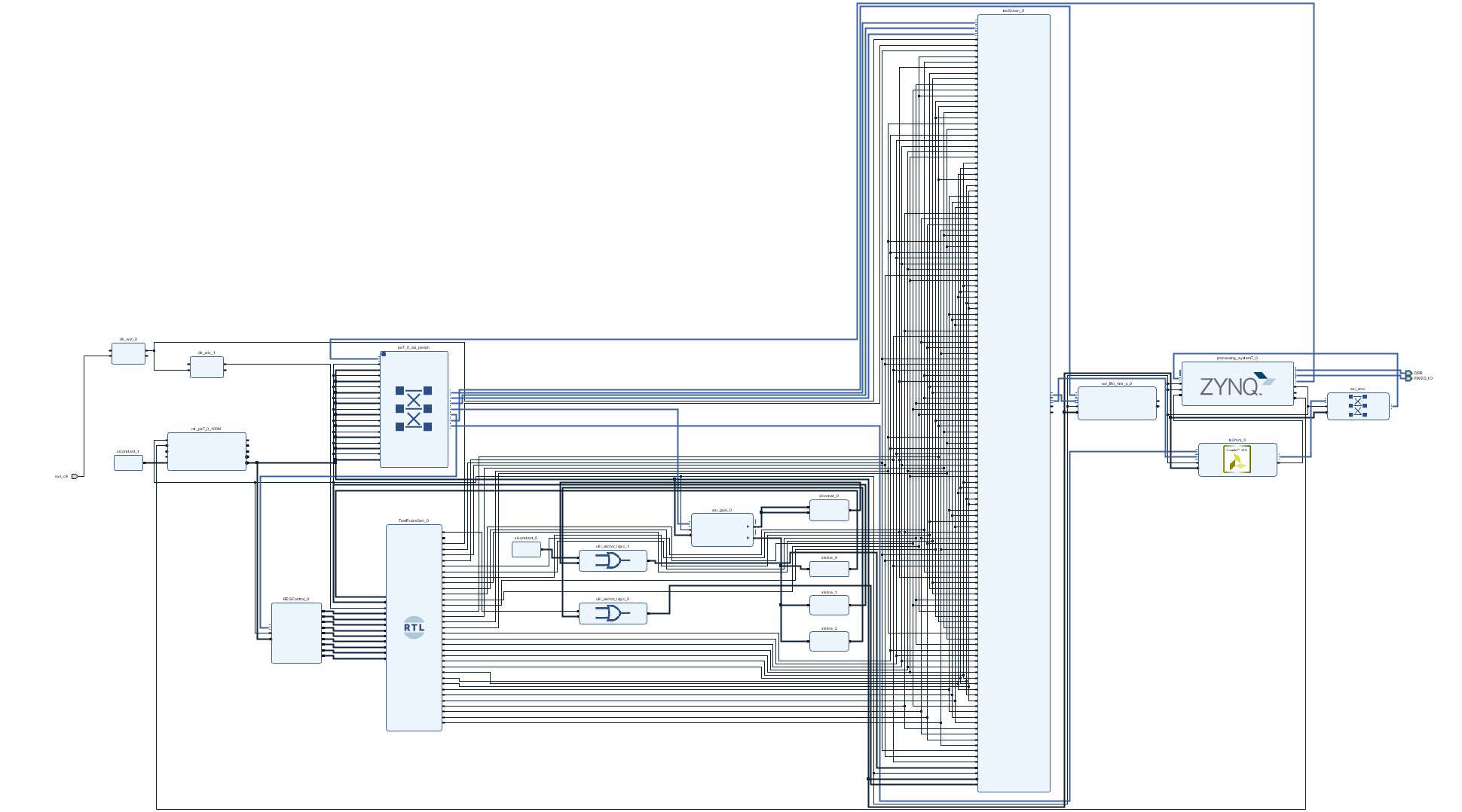

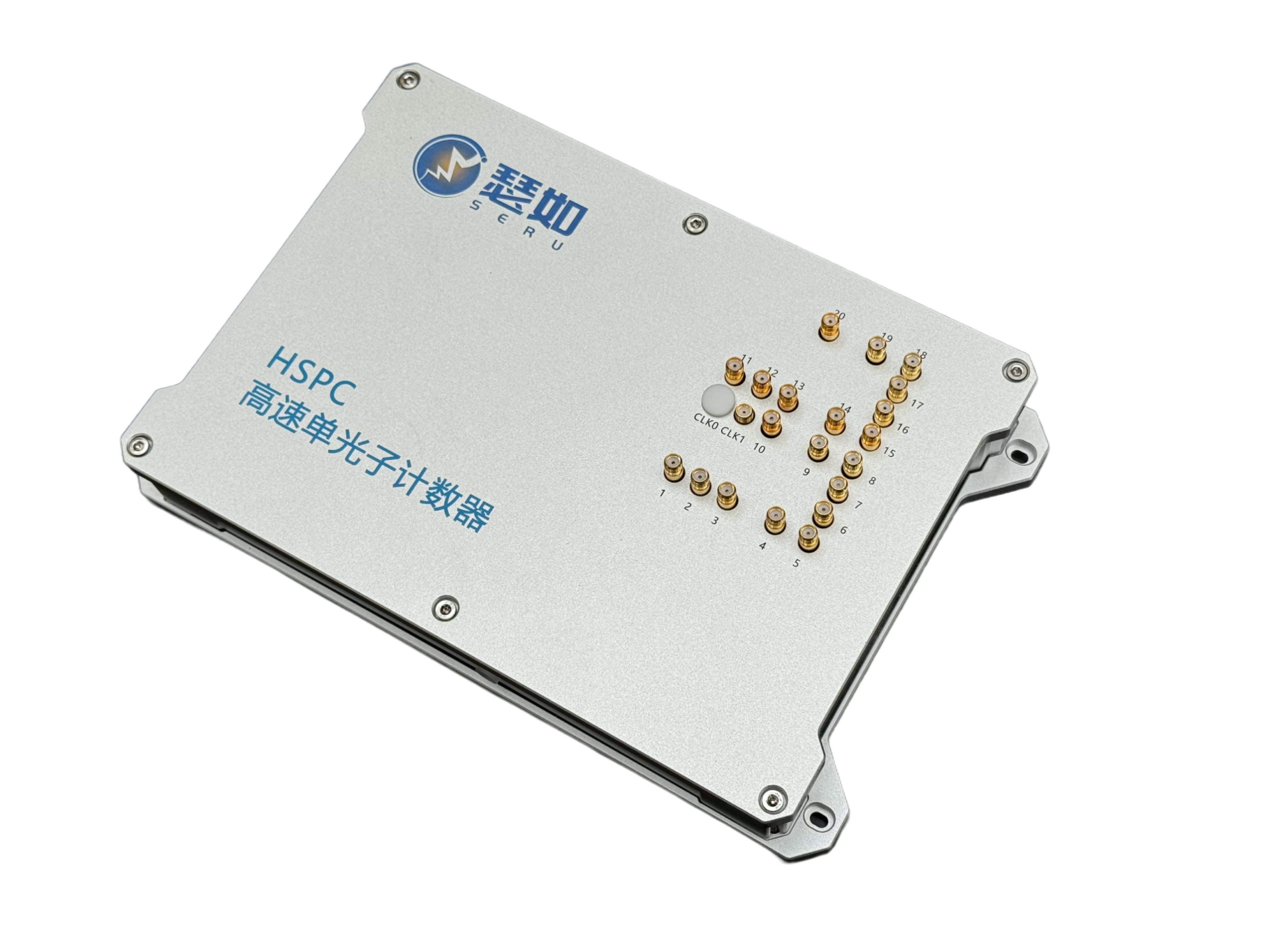

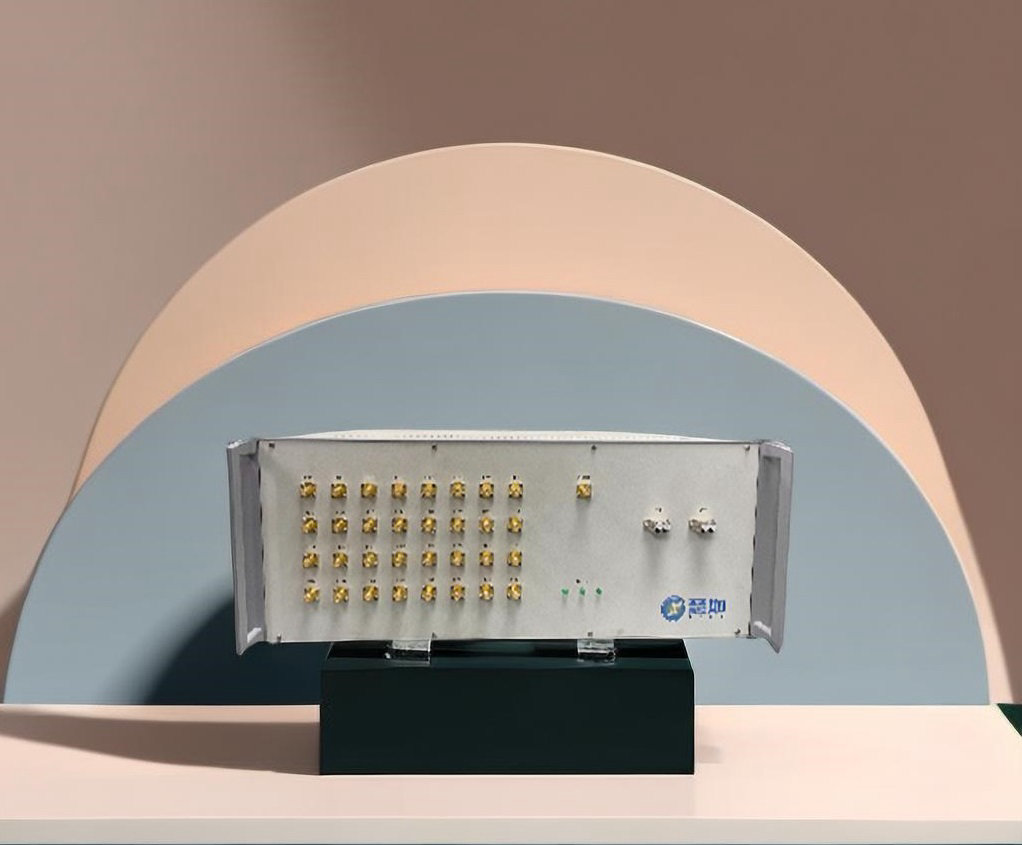

针对市场上对多通道、高速率TDC的需求,瑟如电子对原有73年量程的TDC产品进行了适应性改进。根据激光雷达和PET的需求减小测量量程,输出时间戳的位宽也从96bit减小到了32bit。从而大大减小了TDC IP对FPGA逻辑资源的需求,从而能够在单片FPGA/SOC集成128通道甚至256通道。

评估版TDC IP的默认输入时钟为100MHz,内部通过mmcm产生TDC参考时钟。 也可以在外部配置时钟产生芯片(如Si5338),产生TDC参考时钟,从而能够在整个测量范围内实现严苛的测量精度(<20ps)。

IP具备时钟使能管脚。 在不需要进行测量时可以关闭时钟使能,从而降低功耗。

IP具备通道使能管脚。可以在预期的测量区间外关闭通道使能,从而避免杂波干扰。

每个测量通道包含16点高速FIFO(缓存), 能够充分应对多回波的测量需求。 如有特殊需求,也可定制FIFO点数。

每个通道输出的时间戳经轮询后汇聚一路输出,输出时间戳默认最大频率为100MHz。相当于每秒输出1亿个测量值(100Msps)。可定制多路输出,轻松实现800Msps的时间戳输出频率。

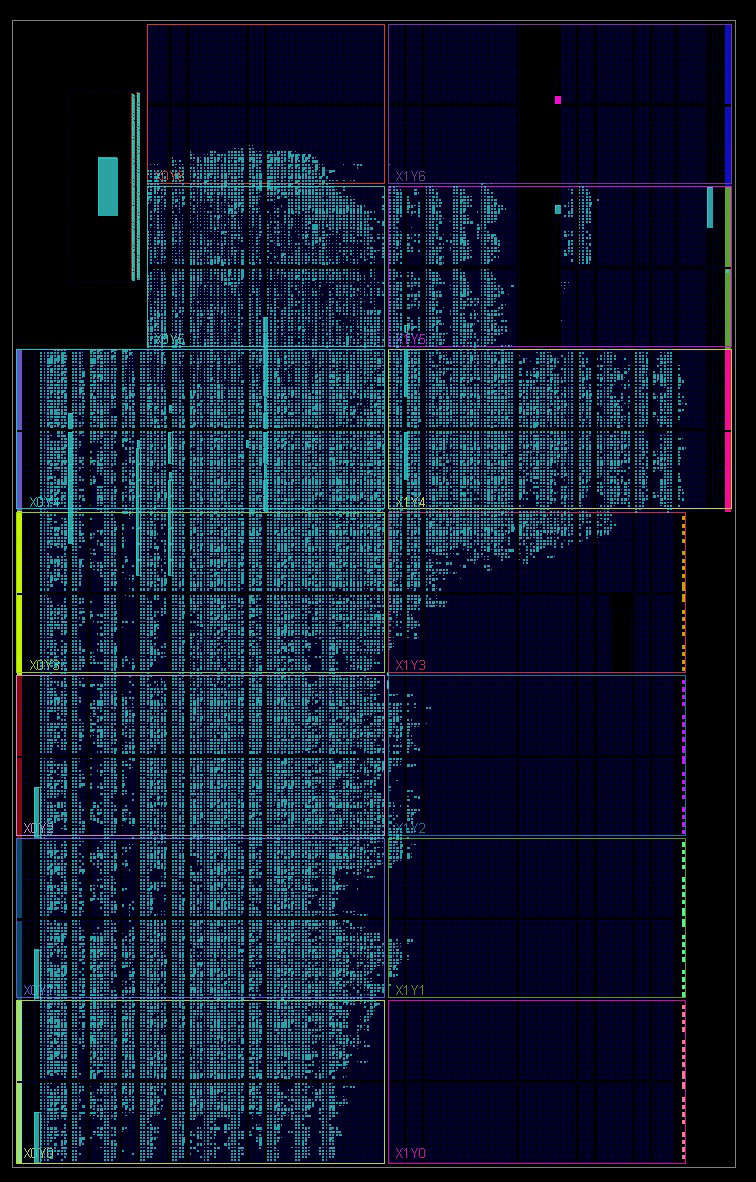

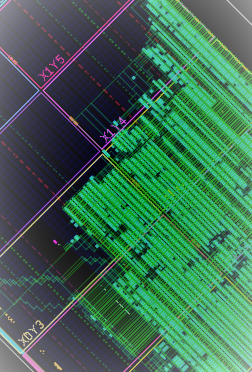

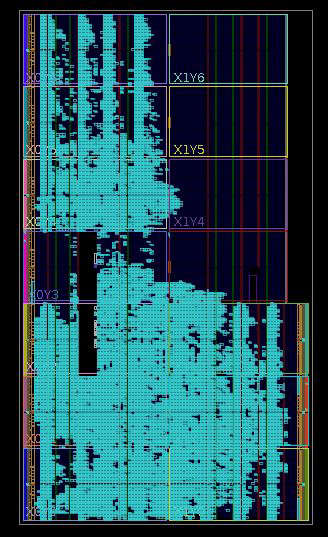

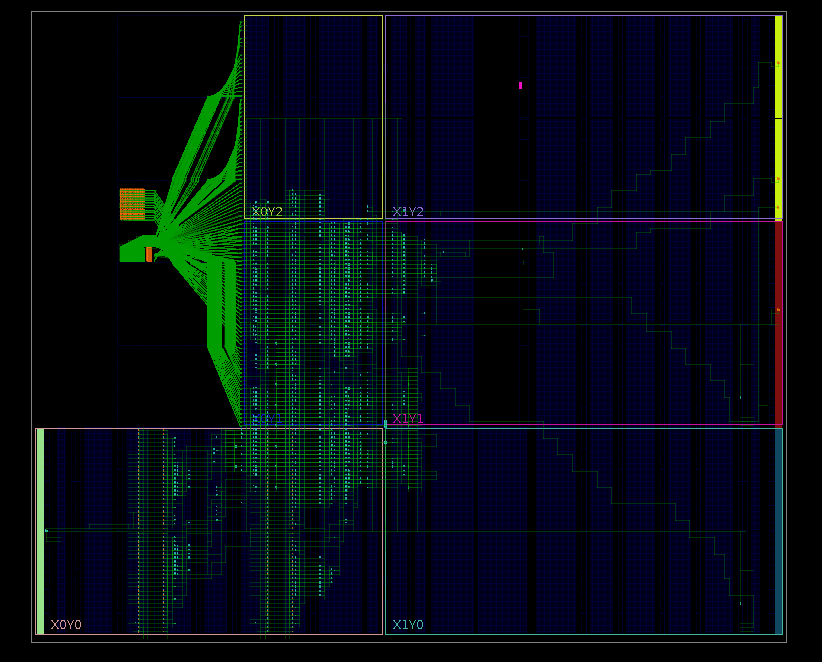

资源占用率(Zynq 7035 129通道TDC 演示工程 ):

请致电18917076612或添加微信14223553 (周工)了解详情。