采用瑟如TDC实现高精度双向时间比对(四)--测试结果分析

同源时钟测试

在同源时钟测试中,测试了3种情况下,双向时间比对的性能,计算了主从时钟时差和路径时延,并进行性能评估,汇总如下表:

序号 | 电缆长度 | 主从时差 均值 (ns) | 主从时差 标准差(ps) | 路径时延 均值 (ns) | 路径时延 标准差 (ps) |

1 | X(未知) | 12322831532.005 | 15.0 | 5.98 | 16.5 |

2 | X+15cm | 3191842744.288 | 14.5 | 6.84 | 16.1 |

3 | X+100cm | 24323933189.302 | 13.3 | 10.91 | 15.8 |

说明:由于每次测试,都对主从板进行重启、下载,因此每次测试的主从时钟时差并不一致。

可以计算得到:标称15cm电缆的时延为6.84-5.98=0.86ns, 标称100cm电缆的时延为10.91-5.98=4.93ns。在同源时钟下,主从时差的比对结果抖动都要优于20ps。路径时延的计算值抖动也优于20ps。

在不同源时钟测试中,测试了3种情况下,双向时间比对的性能,计算了主从时钟时差和路径时延,并进行性能评估,汇总如下表:

序号 | 电缆长度 | 主从时差 均值 (ns) | 主从频差 | 路径时延 均值 (ns) | 路径时延 标准差 (ps) |

1 | X(未知) | 14750070426.789 | 8.12e-6 | 5.98 | 22.2 |

2 | X+15cm | 33112889039.096 | 8.39e-6 | 6.75 | 37.2 |

3 | X+100cm | 14452683955.700 | 8.46e-6 | 10.86 | 20.0 |

当主从开发板时钟不同源时,可以从主从钟差比对结果中很容易的看到,主从时钟存在频率偏差,频差约为8ppm,符合Si5338时钟生成板上25MHz时钟源的参数指标。从路径时延的计算结果可以看出,尽管主从时钟存在较大频率偏差,但对路径时延的计算结果影响有限。因为本方案中,往返脉冲的间隔很短,在10us以内,因此频率偏差造成的相位误差在数十皮秒以内。

不断电换线测试

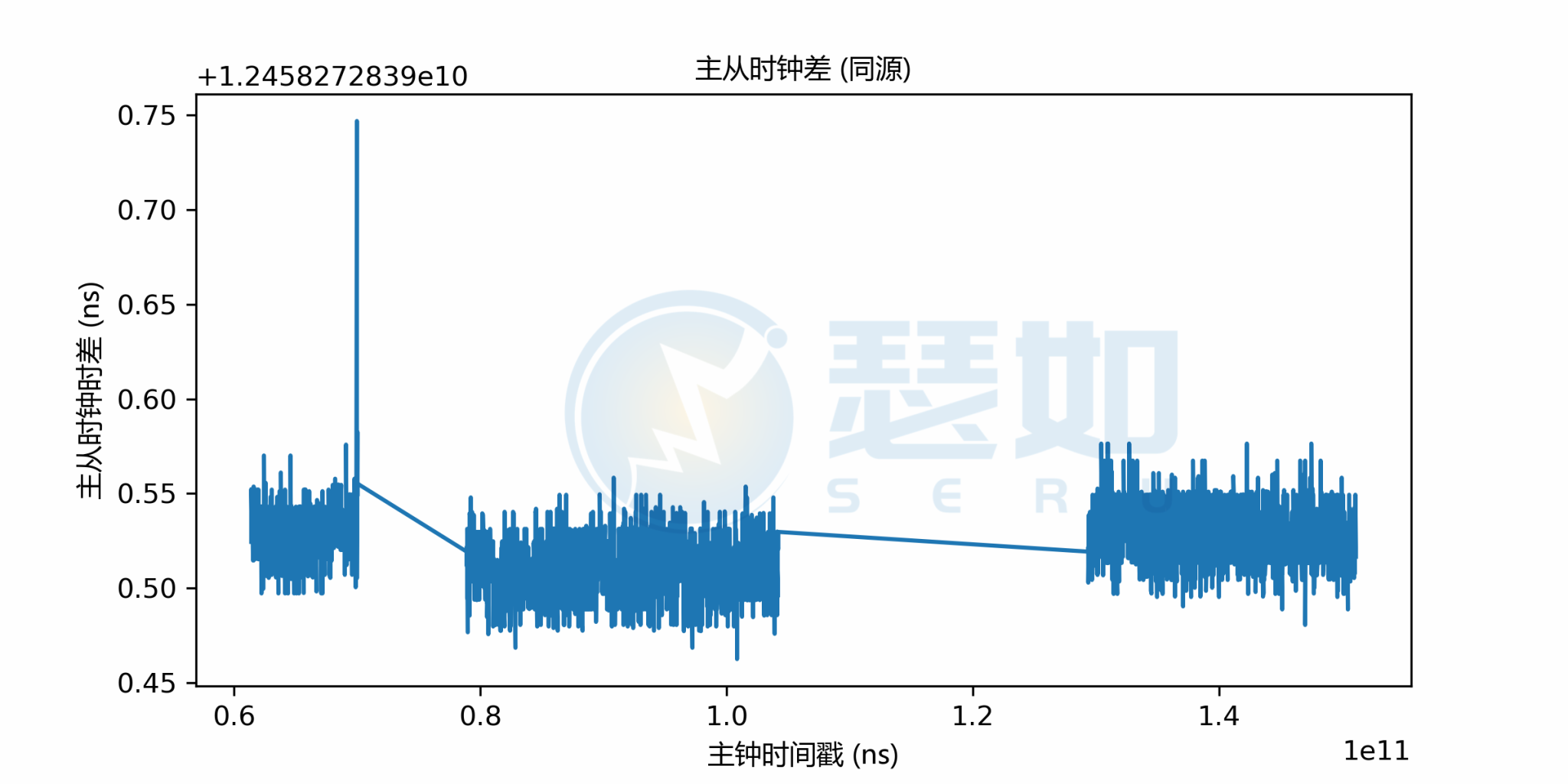

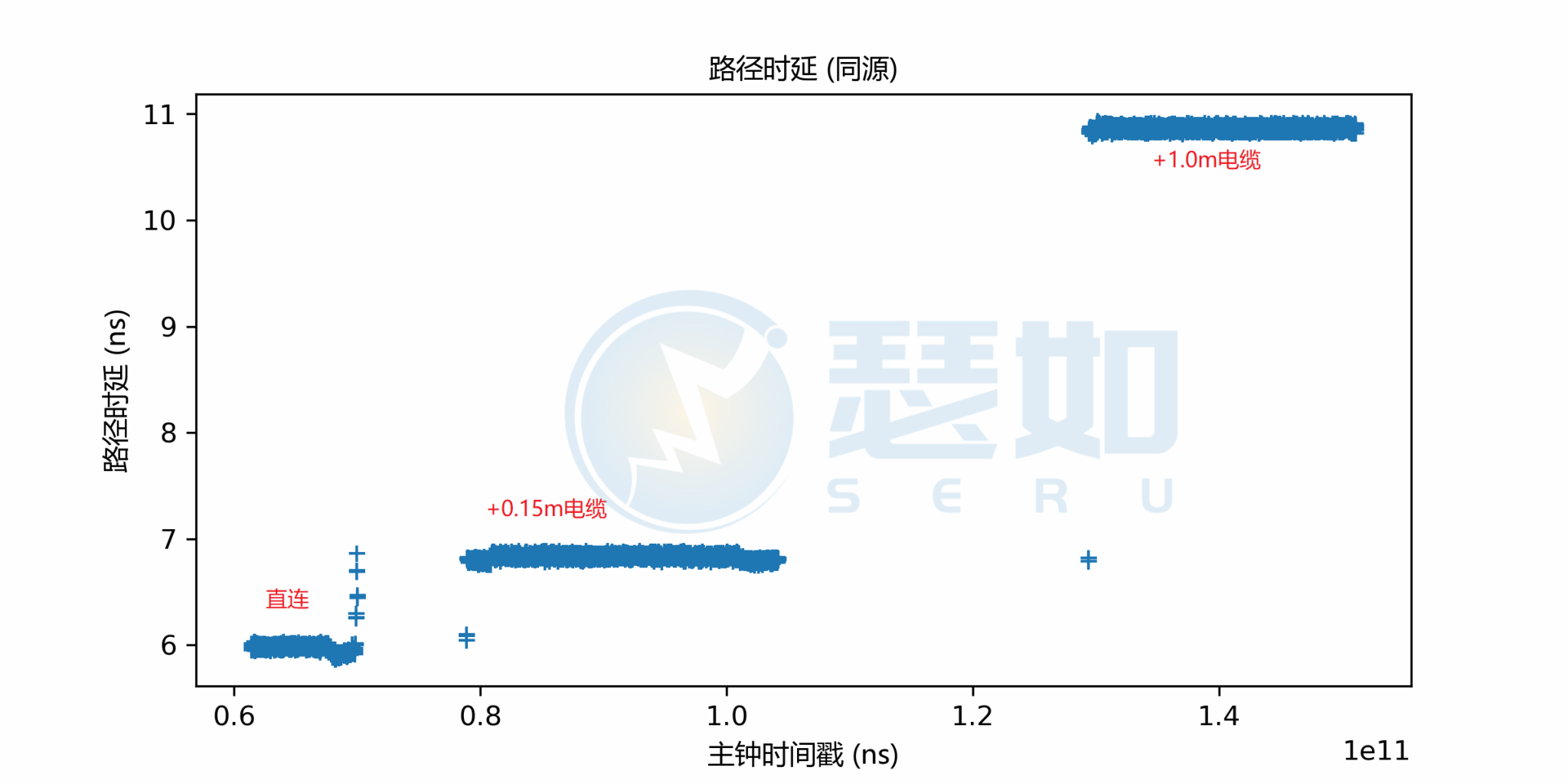

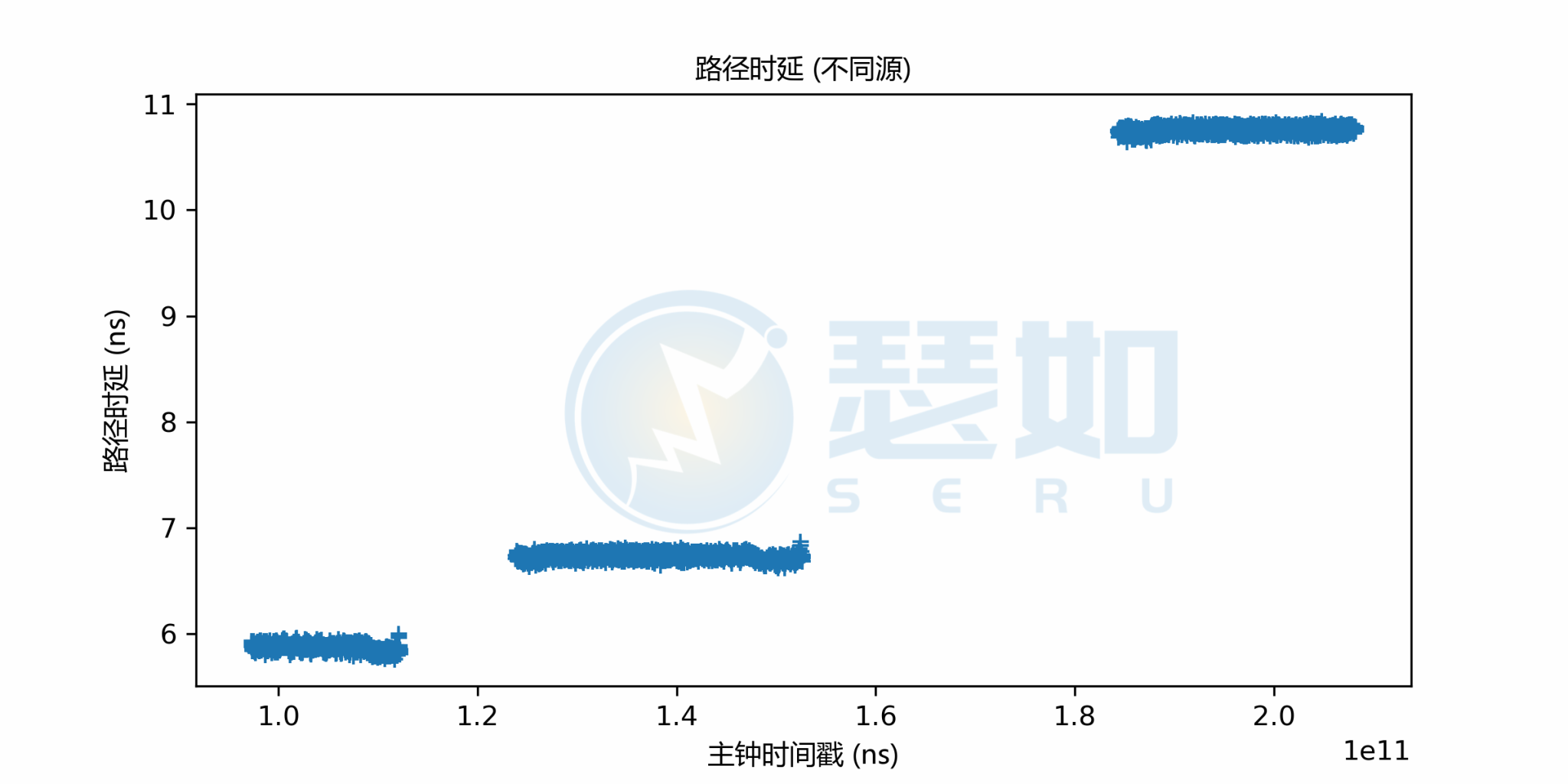

在增加了断线重连的算法后,可以在主从板不断电的情况下更换双向比对的电缆,从而不中断主从板的时钟。从下图可以看到,在直连的情况下,分别增加了0.15m和1m的电缆后,主从时差基本不变,路径时延发生了相应的变化。

同源换线--主从时差

同源换线--路径时延

不同源换线--主从时差

不同源换线--主从时差

最新动态

- 采用瑟如TDC实现高精度双向时间比对(四)--测试结果分析 2019-11-02 15:10:15

- 采用瑟如TDC实现高精度双向时间比对(三)--实验数据 2019-11-01 23:28:42

- 采用瑟如TDC实现高精度双向时间比对(二)--实验设置 2019-11-01 23:00:57

- 采用瑟如TDC实现高精度双向时间比对(一)-- 基本原理 2019-11-01 22:07:19

- TDC PL侧译码单元准备就绪! 2020-11-16 16:10:20

- SeruTek TDC在Kintex上实现160MHz的单通道连续触发! 2020-07-12 22:52:27

- 瑟如电子现提供双通道TDC IP Core,开放免费评估 2020-06-17 11:09:34

- 瑟如电子科技发布基于Xilinx 7 Seriers FPGA/SoC的TDC产品 2019-10-08 08:53:05