上海瑟如电子科技有限公司

采用瑟如TDC实现高精度双向时间比对(一)-- 基本原理

采用SeRuTDC实现20ps的时间比对精度

TDC技术

/ 2019-11-01 22:07:19

《采用瑟如TDC实现高精度双向时间同步》将以连载的形式,用5篇左右的篇幅从多方面介绍双向时间比对的基本原理、实验设置、实验结果分析以及实现过程中一些Vivado、SDK、LwIP的一些技术细节。本篇是该系列的第一篇,介绍双向时间比对的基本原理。

SeRuTDC采用粗计数结合精细计数精密来实现时间戳功能,默认配置下具备长达70年的计时范围,时间戳精度优于20皮秒。在本应用中,采用SeRuTDC core实现主节点和从节点之间的时间同步,并可实时监测主从节点间的路径时延。采用的机制与IEEE1588采用的双向同步方法类似,借助于SeRuTDC 20ps 的时间戳精度,最终得到的时间同步精度、路径时延精度优于50ps,典型值为20ps,大大优于现有的IEEE1588时间同步精度(10ns~1us)。

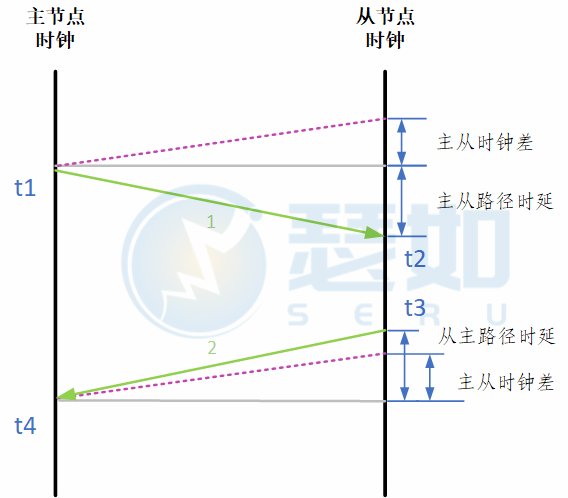

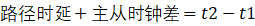

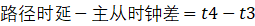

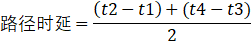

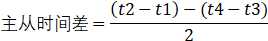

进行双向时间比对时,基本的信号流向如上图。主节点先发送脉冲信号至从节点,从节点收到脉冲信号后,发送脉冲信号至主节点。主从节点各配有一个TDC时间戳模块,记录脉冲信号离开本节点以及脉冲信号到达本节点的时间戳。当主节点发送脉冲信号至从节点时,主节点记录脉冲离开时刻t1, 从节点记录脉冲到达时间t2。从节点发送脉冲信号至主节点时,从节点记录节点离开时刻t3, 主节点记录脉冲到达时刻t4。根据上图,记录的4个时间戳与主从时钟差以及路径时延的关系有:

通过简单的变换可以得到:

最新动态

- 采用瑟如TDC实现高精度双向时间比对(四)--测试结果分析 2019-11-02 15:10:15

- 采用瑟如TDC实现高精度双向时间比对(三)--实验数据 2019-11-01 23:28:42

- 采用瑟如TDC实现高精度双向时间比对(二)--实验设置 2019-11-01 23:00:57

- 采用瑟如TDC实现高精度双向时间比对(一)-- 基本原理 2019-11-01 22:07:19

- TDC PL侧译码单元准备就绪! 2020-11-16 16:10:20

- SeruTek TDC在Kintex上实现160MHz的单通道连续触发! 2020-07-12 22:52:27

- 瑟如电子现提供双通道TDC IP Core,开放免费评估 2020-06-17 11:09:34

- 瑟如电子科技发布基于Xilinx 7 Seriers FPGA/SoC的TDC产品 2019-10-08 08:53:05